Journal of Engineering Research and Reports

14(4): 1-4, 2020; Article no.JERR.57254 ISSN: 2582-2926

# Effect of Backgrinding Tape Lamination on Die Alignment

Bryan Christian Bacquian<sup>1\*</sup> and Frederick Ray Gomez<sup>1</sup>

<sup>1</sup>New Product Development & Introduction, STMicroelectronics, Inc., Calamba City, Laguna, 4027, Philippines.

Authors' contributions

This work was carried out in collaboration between both the authors. Both authors read, reviewed, and approved the final manuscript.

#### Article Information

DOI: 10.9734/JERR/2020/v14i417129 <u>Editor(s)</u>: (1) Dr. Siamak Hoseinzadeh, University of Pretoria, South Africa. (2) Dr. Guang Yih Sheu, Chang-Jung Christian University, Taiwan. (3) Dr. Raad Yahya Qassim, Federal University of Rio de Janeiro, Brazil. (1) Raheel Muzzammel, University of Lahore, Pakistan. (2) S. P. Pandey, Teerthankar Mahaveer University, India. Complete Peer review History: <u>http://www.sdiarticle4.com/review-history/57254</u>

Original Research Article

Received 01 May 2020 Accepted 07 July 2020 Published 21 July 2020

#### ABSTRACT

The continuing growth and development on semiconductor package miniaturization have become a particular interest and focus semiconductor industry. The importance of thinner packages also demands a thinner vertical structure of the integrated circuit (IC) design with silicon die or the wafer playing essential role in package thinning. As the wafer goes thinner, problems may occur in the wafer preparation or pre-assembly. With the introduction of new wafer preparation technologies such as dicing before grinding and laser die attach film (DAF) cut, technical challenges were inevitable. The paper focused on the effect of backgrinding tape lamination on die alignment. Tensionless lamination helped eliminate the horizontal pressure applied into the tape thus mitigating the die mis-alignment problem. For future works, the configuration could be applied on wafers with similar technology and/or application.

Keywords: Lamination; backgrinding; wafer thinning; die alignment.

\*Corresponding author: Email: bryan-christian.bacquian@st.com;

#### **1. INTRODUCTION**

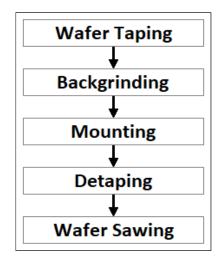

Every new technology developed and introduced in the manufacturing plant brings along many challenges that would affect the assembly yield. The development of thinner die configuration has evolved from the conventional wafer preparation process into an advanced dicing before grinding process. Traditional pre-assembly or wafer preparation process shown in Fig. 1 involves taping, backgrinding, wafer until wafer mechanical sawing. Worthy to note that manufacturing assembly process flow differs with the product and its technology [1-4]. With the continuing technology trends and state-of-the-art platforms, challenges in semiconductor assembly manufacturing are inevitable [5-7]. The paper focused on the effect on die alignment with different types of backgrinding tape lamination.

Fig. 1. Pre-assembly conventional process flow

# 2. LITERATURE REVIEW AND PROBLEM IDENTIFICATION

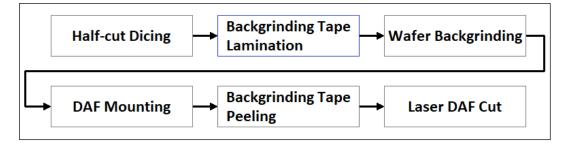

Dicing before grinding was introduced to attain the required thin wafer thickness without compromising the die strength. The process is focused on the removal of backside chipping which might cause breakage on the silicon area of the die, consequently improving the silicon die's quality [8]. Nevertheless, the process is not enough to support the increasing demand for thinner packages. The addition of the die attach film (DAF) material attached underneath the presawn grinded wafer brought another challenge for a breakthrough process development which is the laser DAF cut. Laser (light amplification by stimulated emission or radiation) DAF cut is focused on the successive singulation of the DAF material underneath the pre-sawn wafer using low power lasers. With this, the introduction of dicing before grinding with laser DAF cut would enable the integration of the wafer thinning process and the use of DAF without compromising the quality requirement of thinner dice [8]. Fig. 2 shows the wafer preparation process flow including the laser DAF cut.

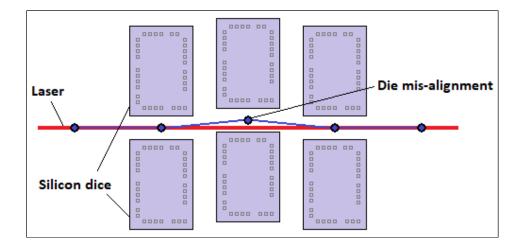

One advantage of laser DAF cut is the ability not to subject the silicon wafer and DAF to any mechanical stress thus removing the possibility of chippings or burrs. The laser will pass through the die opening (kerf width) without hitting the silicon side wall thus eliminating mechanical stress. On the other hand, an inherent problem encountered at the advanced pre-assembly process is the die mis-alignment or kerf shifting as illustrated in Fig. 3. Kerf shifting refers to the movement of dice induced after wafer backgrinding and mounting process. The higher the tension being applied to the wafer, the higher disturbance into the singulated dice would happen. This in turn result to the die movement or mis-alignment. The control of tension during the dicing before grinding process should be carefully employed. Along with the tension applied during backgrinding tape lamination, stress added during succeeding processes increases concern for die shifting issues.

Fig. 2. Advanced pre-assembly process flow

Fig. 3. Die mis-alignment manifestation

## **3. EXPERIMENTATION**

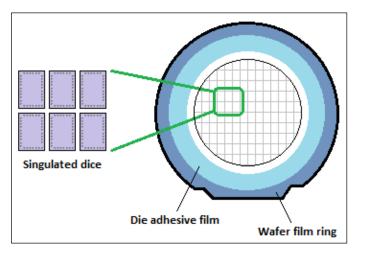

Silicon wafer with DAF was used as carrier for the evaluation as represented in Fig. 4. Wafers were processed using the dicing before grinding process with 50 microns specified final thickness and a required final die size.

The evaluation done to understand and solve the large die mis-alignment issue is categorized into backgrinding tape lamination tension effect validation using tension and tensionless lamination process. To check the robustness of the wafer during backgrinding with different backgrinding tape lamination condition, one tape was used throughout the experiment. The effect would be distinguished using different conditions, with tension and tensionless lamination. Tension lamination refers to the standard backgrinding tape lamination process wherein pressure is applied horizontally and vertically with respect to surface. Conversely, tensionless wafer lamination refers to the process wherein backgrinding tapes are applied without any tension or pressure. The experiment results were then assessed based on the large die misalignment.

#### Fig. 4. Wafer representation

| Tab | le 1 | . Eva | luatio | on on | bac | kgri | indi | ng t | tape | lami | nati | on |

|-----|------|-------|--------|-------|-----|------|------|------|------|------|------|----|

|-----|------|-------|--------|-------|-----|------|------|------|------|------|------|----|

| Type of lamination | Die mis-alignment | Remarks |  |

|--------------------|-------------------|---------|--|

| With tension       | Manifested        | Fail    |  |

| Tensionless        | No manifestation  | Pass    |  |

#### 4. RESULTS AND DISCUSSION

The experiment results were analyzed on the different evaluation trials. Table 1 showsat tensionless lamination helped eliminate the horizontal pressure applied onto thetape thus mitigating the die mis-alignment issue.

With the die mis-alignment problem addressed during backgrinding tape lamination, other wafer defect particularly edge cutting was also eliminated.

#### 5. CONCLUSION AND RECOMMENDA-TIONS

Tension control is the critical characteristics on handling thin wafers processed using dicing before grinding process. Tensionless backgrinding tape lamination is vital fordie alignment control which helped eliminate the horizontal pressure applied on the tape, hence preventing the die mis-alignment problem.

Future studies could include some failure cases to validate the application on wafers. Discussions in [9-11] are helpful in mitigating defects related to wafer preparation. In-depth evaluation on different tapes and sizes, as well as tension control mechanism and applied pressure could be explored. Forfuture works, tensionless type of lamination could similar be applied on wafers with dietechnology.

#### ACKNOWLEDGEMENT

The authors would like to express appreciation to the New Product Development & Introduction (NPD-I) team and the Management Team for the countless support.

## **COMPETING INTERESTS**

Authors have declared that no competing interests exist.

#### REFERENCES

- 1. Harper C. Electronic packaging and interconnection handbook. 4<sup>th</sup> ed., McGraw-Hill Education, USA; 2004.

- Geng H. Semiconductor manufacturing handbook. 2<sup>nd</sup> ed., McGraw-Hill Education, USA; 2017.

- 3. Nenni D, McLellan P. Fabless: the transformation of the semiconductor industry. CreateSpace Independent Publishing Platform, USA; 2014.

- May GS, Spanos CJ. Fundamentals of semiconductor manufacturing and process control. 1<sup>st</sup> ed., Wiley-IEEE Press, USA; 2006.

- 5. Tsukada Y, Kobayashi K, Nishimura H. Trend of semiconductor packaging, high density and low cost. 4th International Symposium on Electronic Materials and Packaging, Taiwan; 2002.

- Xian TS, Nanthakumar P. Dicing die attach challenges at multi die stack packages. 35th IEEE/CPMT International Electronics Manufacturing Technology Conference, Malaysia; 2012.

- Liu Y, Irving S, Luk T, Kinzer D. Trends of power electronic packaging and modeling. 10th Electronics Packaging Technology Conference, Singapore; 2008.

- Disco Corporation. Dicing before grinding process + laser daf cut. Available:http://www.disco.co.jp/eg/solutio n/library/dbg\_daf.html

- Bacquian BC, Gomez FR. A study of wafer backgrinding tape selection for SOI wafers. Journal of Engineering Research and Reports.2019;6(2):1-6.

- Sumagpang Jr.A, Gomez FR. Line stressing critical processes optimization of scalable package passive device for successful production ramp-up. Journal of Engineering Research and Reports. 2018;3(1):1-13.

- Bacquian BC, Gomez FR. A study of vacuum efficiency for silicon on insulator wafers. Journal of Engineering Research and Reports. 2019;6(1):1-6.

© 2020 Bacquian and Gomez; This is an Open Access article distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/4.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

> Peer-review history: The peer review history for this paper can be accessed here: http://www.sdiarticle4.com/review-history/57254